分类: 产业资讯

在高密度多PIN连接器的应用中,信号干扰和信号完整性问题是设计和生产中常见的挑战。LOTES作为领先的连接器制造商,提供多种高精密连接器,广泛应用于服务器、汽车电子和消费电子等领域。本文将探讨如何在使用LOTES多PIN连接器时优化信号完整性,减少干扰,提高系统性能。

一、LOTES连接器概述

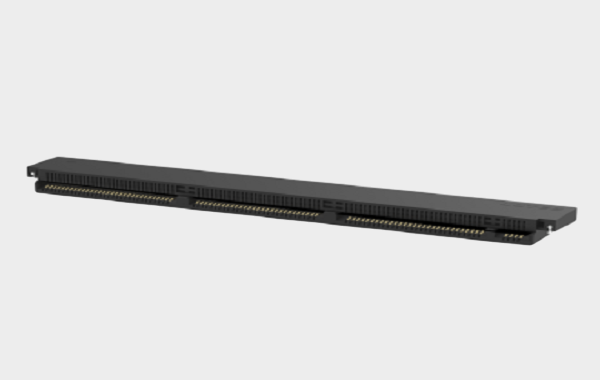

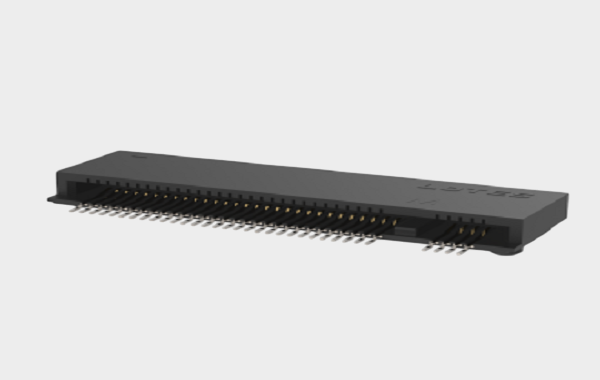

LOTES成立于1986年,总部位于台湾基隆市,是全球领先的高精密电子互连组件制造商。公司产品涵盖CPU插座、内存插座、板对板连接器、汽车电子连接器等,广泛应用于计算机、服务器、汽车电子和消费电子领域。LOTES以高可靠性焊脚设计、精密贴合结构和全流程质量管理著称,产品稳定可靠,能够满足高标准应用需求。

--------------------------------------------------------------------------------------

二、多PIN连接器信号干扰的原因

在多PIN连接器中,信号干扰主要来源于以下几个方面:

1. 信号线间距过小:高密度的引脚布局可能导致信号线之间串扰,影响信号质量。

2. 地线设计不合理:地线不连续或不完整可能导致地电位波动,增加噪声。

3. 电源分配不均:电源线与信号线布局不当可能引入电源噪声,影响信号稳定性。

4. PCB布局不当:不合理的PCB布局可能导致信号路径过长或不对称,增加信号衰减和反射。

--------------------------------------------------------------------------------------

三、优化信号完整性的设计技巧

为减少多PIN连接器中的信号干扰,可以采取以下设计策略:

1. 合理布局信号线:增加信号线之间间距,减少串扰。

2. 优化地线设计:确保地线连续且宽度足够,减少地电位波动。

3. 均匀电源分配:设计合理的电源分配网络,减少电源噪声对信号的影响。

4. 对称布线:尽量保持信号路径的对称性,减少信号反射和衰减。

5. 使用屏蔽技术:在高频信号线周围使用屏蔽层,减少外部干扰。

--------------------------------------------------------------------------------------

四、LOTES连接器的信号完整性优势

LOTES的多PIN连接器在设计和制造过程中充分考虑了信号完整性问题,具有以下优势:

1. 精密的引脚间距:合理的引脚间距设计,减少信号线之间串扰。

2. 优质接触材料:采用优质接触材料,降低接触电阻,提高信号传输质量。

3. 优化的焊脚设计:精密焊脚设计,确保良好焊接质量,减少信号损耗。

4. 严格质量控制:全流程质量管理,确保产品稳定性和可靠性。

在多PIN连接器的应用中,信号干扰和完整性问题是不可忽视的挑战。通过合理的设计和优化,可以有效减少这些问题,提高系统的性能和稳定性。LOTES作为领先的连接器制造商,其产品在信号完整性方面具有明显优势,是高性能系统设计的理想选择。

若您有该品牌连接器的代理、销售渠道或库存资源,或有采购需求,欢迎联系张经理:18665383950(微信同号),我们资源共享、合作共赢。